Products Kategorya

- FM transmiter

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV transmiter

- 0-50w 50-1kw 2kw-10kw

- FM Antenna

- TV Antenna

- antenna Accessory

- Kable connector Power Splitter dummy load

- RF transistor

- Power Supply

- Audio Equipments

- DTV Front End Equipment

- link System

- STL sistema Microwave Link sistema

- FM Radio

- Power Meter

- Ibang produkto

- Espesyal para sa Coronavirus

Produkto Tags

Fmuser Sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> Albanian

- ar.fmuser.net -> Arabe

- hy.fmuser.net -> Armenian

- az.fmuser.net -> Azerbaijani

- eu.fmuser.net -> Basque

- be.fmuser.net -> Belarusian

- bg.fmuser.net -> Bulgarian

- ca.fmuser.net -> Catalan

- zh-CN.fmuser.net -> Intsik (Pinasimple)

- zh-TW.fmuser.net -> Intsik (Tradisyunal)

- hr.fmuser.net -> Croatian

- cs.fmuser.net -> Czech

- da.fmuser.net -> Danish

- nl.fmuser.net -> Dutch

- et.fmuser.net -> Estonian

- tl.fmuser.net -> Pilipino

- fi.fmuser.net -> Finnish

- fr.fmuser.net -> Pranses

- gl.fmuser.net -> Galician

- ka.fmuser.net -> Georgian

- de.fmuser.net -> Aleman

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haitian Creole

- iw.fmuser.net -> Hebrew

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Hungarian

- is.fmuser.net -> Icelandic

- id.fmuser.net -> Indonesian

- ga.fmuser.net -> Irish

- it.fmuser.net -> Italian

- ja.fmuser.net -> Japanese

- ko.fmuser.net -> Koreano

- lv.fmuser.net -> Latvian

- lt.fmuser.net -> Lithuanian

- mk.fmuser.net -> Macedonian

- ms.fmuser.net -> Malay

- mt.fmuser.net -> Maltese

- no.fmuser.net -> Norwegian

- fa.fmuser.net -> Persian

- pl.fmuser.net -> Polish

- pt.fmuser.net -> Portuges

- ro.fmuser.net -> Romanian

- ru.fmuser.net -> Ruso

- sr.fmuser.net -> Serbiano

- sk.fmuser.net -> Slovak

- sl.fmuser.net -> Slovenian

- es.fmuser.net -> Espanyol

- sw.fmuser.net -> Swahili

- sv.fmuser.net -> Suweko

- th.fmuser.net -> Thai

- tr.fmuser.net -> Turkish

- uk.fmuser.net -> Ukrainian

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> Vietnamese

- cy.fmuser.net -> Welsh

- yi.fmuser.net -> Yiddish

PMOS at NMOS Transistors

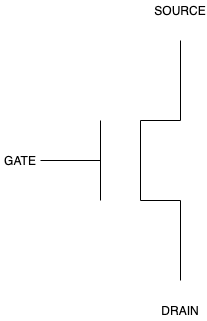

Ang mga microprocessor ay binuo ng mga transistor. Sa partikular, ang mga ito ay itinayo mula sa MOS transistors. Ang MOS ay isang acronym para sa Metal-Oxide Semiconductor. Mayroong dalawang uri ng MOS transistors: pMOS (positive-MOS) at nMOS (negative-MOS). Ang bawat pMOS at nMOS ay nilagyan ng tatlong pangunahing bahagi: ang gate, ang source, at ang drain.

Upang maayos na maunawaan kung paano gumagana ang isang pMOS at isang nMOS, mahalagang tukuyin muna ang ilang termino:

closed-circuit: Nangangahulugan ito na ang kuryente ay dumadaloy mula sa gate patungo sa pinagmulan.

open-circuit: Nangangahulugan ito na ang kuryente ay hindi dumadaloy mula sa gate patungo sa pinagmulan; pero sa halip, may dumadaloy na kuryente mula sa gate hanggang sa drain.

Kapag ang isang nMOS transistor ay nakatanggap ng isang hindi bale-wala na boltahe, ang koneksyon mula sa pinagmulan patungo sa alisan ng tubig ay nagsisilbing isang wire. Daloy ang kuryente mula sa pinagmumulan patungo sa drain nang walang harang — ito ay tinutukoy bilang closed-circuit. Sa kabilang banda, kapag ang isang nMOS transistor ay nakatanggap ng boltahe sa humigit-kumulang 0 volts, ang koneksyon mula sa pinagmulan patungo sa alisan ng tubig ay masisira at ito ay tinutukoy bilang isang open-circuit.

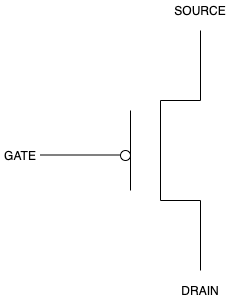

Ang p-type na transistor ay gumagana nang eksaktong kontra sa n-type na transistor. Samantalang ang nMOS ay bubuo ng closed-circuit na may pinagmulan kapag ang boltahe ay hindi bale-wala, ang pMOS ay bubuo ng isang open-circuit na may pinagmulan kapag ang boltahe ay hindi bale-wala.

Tulad ng makikita mo sa larawan ng pMOS transistor na ipinakita sa itaas, ang tanging pagkakaiba sa pagitan ng isang pMOS transistor at isang nMOS transistor ay ang maliit na bilog sa pagitan ng gate at ng unang bar. Binabaligtad ng bilog na ito ang halaga mula sa boltahe; kaya, kung ang gate ay nagpapadala ng isang boltahe na kinatawan ng isang halaga ng 1, pagkatapos ay ang inverter ay baguhin ang 1 sa isang 0 at maging sanhi ng circuit upang gumana nang naaayon.

Dahil ang pMOS at nMOS ay gumagana sa isang kabaligtaran na paraan — sa isang pantulong na paraan — kapag pinagsama natin ang dalawa sa isang higanteng MOS circuit, ito ay tinatawag na cMOS circuit, na kumakatawan sa komplementaryong metal-oxide semiconductor.

Paggamit ng MOS Circuits

Maaari nating pagsamahin ang mga circuit ng pMOS at nMOS upang makabuo ng mas kumplikadong mga istruktura na tinatawag na GATES, mas partikular: mga gate ng lohika. Naipakilala na namin ang konsepto ng mga lohikal na function na ito at ang nauugnay na mga talahanayan ng katotohanan sa nakaraang blog, na mahahanap mo sa pamamagitan ng pag-click dito.

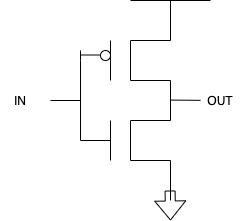

Maaari naming ilakip ang isang pMOS transistor na kumokonekta sa pinagmulan at isang nMOS transistor na kumokonekta sa lupa. Ito ang aming unang halimbawa ng isang cMOS transistor.

Ang cMOS transistor na ito ay kumikilos sa paraang katulad ng NOT logical function.

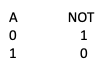

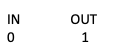

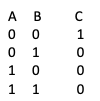

Tingnan natin ang talahanayan ng HINDI katotohanan:

Sa NOT truth table, bawat input value: A ay baligtad. Ano ang mangyayari sa circuit sa itaas?

Well, isipin natin ang input ay isang 0.

Ang 0 ay pumapasok at parehong pataas at pababa sa wire sa parehong pMOS (itaas) at ang nMOS (ibaba). Kapag ang halagang 0 ay umabot sa pMOS, ito ay nababaligtad sa isang 1; kaya, ang koneksyon sa pinagmulan ay sarado. Magbubunga ito ng lohikal na halaga na 1 hangga't hindi rin nakasara ang koneksyon sa lupa (drain). Well, dahil ang mga transistor ay pantulong, alam namin na ang nMOS transistor ay hindi baligtarin ang halaga; kaya, ito ay tumatagal ng halaga 0 bilang ay at - samakatuwid - lumikha ng isang bukas na circuit sa lupa (drain). Kaya, ang isang lohikal na halaga ng 1 ay ginawa para sa gate.

Ano ang mangyayari kung ang isang 1 ay ang halaga ng IN? Buweno, ang pagsunod sa parehong mga hakbang tulad ng nasa itaas, ang halaga 1 ay naipapadala sa parehong pMOS at sa nMOS. Kapag ang halaga ay natanggap ng pMOS, ang halaga ay nababaligtad sa isang 0; kaya, ang koneksyon sa SOURCE ay bukas. Kapag ang halaga ay natanggap ng nMOS, ang halaga ay hindi nababaligtad; kaya, ang halaga ay nananatiling isang 1. Kapag ang isang halaga ng 1 ay natanggap ng nMOS, ang koneksyon ay sarado; kaya, ang koneksyon sa lupa ay sarado. Magbubunga ito ng lohikal na halaga na 0.

Ang pagsasama-sama ng dalawang set ng input/output ay magbubunga ng:

Napakadaling makita na ang talahanayan ng katotohanan na ito ay eksaktong kapareho ng HINDI ginagawa ng lohikal na function. Kaya, ito ay kilala bilang isang NOT gate.

Maaari ba nating gamitin ang dalawang simpleng transistor na ito upang makagawa ng mas kumplikadong mga istruktura? Ganap! Susunod, gagawa tayo ng NOR gate at OR gate.

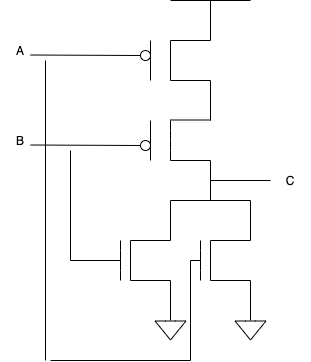

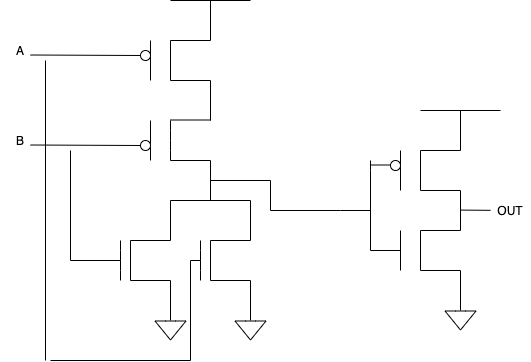

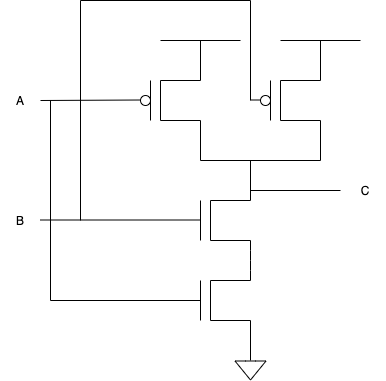

Gumagamit ang circuit na ito ng dalawang pMOS transistors sa itaas at dalawang nMOS transistors sa ibaba. Muli, tingnan natin ang input sa gate upang makita kung paano ito kumikilos.

Kapag ang A ay 0 at ang B ay 0, babaligtarin ng gate na ito ang parehong mga halaga sa isang 1 kapag naabot nila ang mga transistor ng pMOS; gayunpaman, ang mga nMOS transistors ay parehong magpapanatili ng halaga ng 0. Ito ay hahantong sa gate upang makabuo ng isang halaga ng 1.

Kapag ang A ay 0 at B ay 1, babaligtarin ng gate na ito ang parehong mga halaga kapag naabot nila ang mga transistors ng pMOS; kaya, ang A ay magbabago sa 1 at ang B ay magbabago sa 0. Hindi ito hahantong sa pinagmulan; dahil ang parehong mga transistor ay nangangailangan ng isang closed-circuit upang ikonekta ang input sa pinagmulan. Ang mga nMOS transistors ay hindi binabaligtad ang mga halaga; kaya, ang nMOS na nauugnay sa A ay bubuo ng 0, at ang nMOS na nauugnay sa B ay gagawa ng 1; kaya, ang nMOS na nauugnay sa B ay gagawa ng isang closed circuit sa lupa. Ito ay hahantong sa gate upang makabuo ng isang halaga na 0.

Kapag ang A ay 1 at B ay 0, babaligtarin ng gate na ito ang parehong mga halaga kapag naabot nila ang mga transistor ng pMOS; kaya, ang A ay magbabago sa 0at ang B ay magbabago sa 1. Hindi ito hahantong sa pinagmulan; dahil ang parehong mga transistor ay nangangailangan ng isang closed-circuit upang ikonekta ang input sa pinagmulan. Ang mga nMOS transistors ay hindi binabaligtad ang mga halaga; kaya, ang nMOS na nauugnay sa A ay bubuo ng 1, at ang nMOS na nauugnay sa B ay bubuo ng 0; kaya, ang nMOS na nauugnay sa Awill gumawa ng isang closed circuit sa lupa. Ito ay hahantong sa gate upang makabuo ng isang halaga na 0.

Kapag ang A ay 1 at B ay 1, babaligtarin ng gate na ito ang parehong mga halaga kapag naabot nila ang mga transistor ng pMOS; kaya, ang A ay magbabago sa 0 at ang B ay magbabago sa 0. Hindi ito hahantong sa pinagmulan; dahil ang parehong mga transistor ay nangangailangan ng isang closed-circuit upang ikonekta ang input sa pinagmulan. Ang mga nMOS transistors ay hindi binabaligtad ang mga halaga; kaya, ang nMOS na nauugnay sa A ay bubuo ng 1, at ang nMOS na nauugnay sa B ay gagawa ng 1; kaya, ang nMOS na nauugnay sa A at ang nMOS na nauugnay sa B ay gagawa ng isang closed circuit sa lupa. Ito ay hahantong sa gate upang makabuo ng isang halaga na 0.

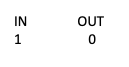

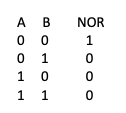

Kaya, ang talahanayan ng katotohanan ng gate ay ang mga sumusunod:

Samantala, ang talahanayan ng katotohanan ng NOR logical function ay ang mga sumusunod:

Kaya, nakumpirma namin na ang gate na ito ay isang NOR gate dahil ibinabahagi nito ang talahanayan ng katotohanan nito sa NOR logical function.

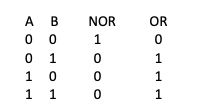

Ngayon, ilalagay natin ang parehong gate, na nilikha natin hanggang ngayon, upang makagawa ng isang OR gate. Tandaan, ang NOR ay nangangahulugang NOT OR; kaya, kung binaligtad natin ang isang nakabaliktad na gate, babalik tayo sa orihinal. Subukan natin ito upang makita ito sa pagkilos.

Ang ginawa namin dito ay kinuha namin ang NOR gate mula sa dati at naglapat ng NOT gate sa output. Tulad ng ipinakita namin sa itaas, ang NOT gate ay kukuha ng halaga na 1 at maglalabas ng 0, at ang NOT gate ay kukuha ng halaga na 0 at maglalabas ng 1.

Dadalhin nito ang mga halaga ng NOR gate at iko-convert ang lahat ng 0s sa 1s at 1s sa 0s. Kaya, ang talahanayan ng katotohanan ay ang mga sumusunod:

Kung gusto mo ng higit pang pagsasanay sa pagsubok sa mga gate na ito, huwag mag-atubiling subukan ang mga halaga sa itaas para sa iyong sarili at makita na ang gate ay gumagawa ng mga katumbas na resulta!

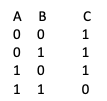

Sinasabi kong ito ay isang gate ng NAND, ngunit subukan natin ang talahanayan ng katotohanan ng gate na ito upang matukoy kung ito ay talagang isang gate ng NAND.

Kapag ang A ay 0 at ang B ay 0, ang pMOS ng A ay gagawa ng 1, at ang nMOS ng A ay gagawa ng 0; kaya, ang gate na ito ay gagawa ng isang lohikal na 1 dahil ito ay konektado sa source na may closed circuit at disconnected mula sa lupa na may isang open circuit.

Kapag ang A ay 0 at ang B ay 1, ang pMOS ng A ay gagawa ng 1, at ang nMOS ng A ay gagawa ng 0; kaya, ang gate na ito ay gagawa ng isang lohikal na 1 dahil ito ay konektado sa source na may closed circuit at disconnected mula sa lupa na may isang open circuit.

Kapag ang A ay 1 at ang B ay 0, ang pMOS ni B ay gagawa ng 1, at ang nMOS ng B ay gagawa ng 0; kaya, ang gate na ito ay gagawa ng isang lohikal na 1 dahil ito ay konektado sa source na may closed circuit at disconnected mula sa lupa na may isang open circuit.

Kapag ang A ay 1 at ang B ay 1, ang pMOS ng A ay gagawa ng 0, at ang nMOS ng A ay gagawa ng isang 1; kaya, dapat nating suriin ang pMOS at nMOS ni B, pati na rin. Ang pMOS ni B ay gagawa ng 0, at ang nMOS ni B ay gagawa ng 1; kaya, ang gate na ito ay magbubunga ng isang lohikal na 0 dahil ito ay nadiskonekta mula sa pinagmulan na may isang bukas na circuit at nakakonekta sa lupa na may isang closed circuit.

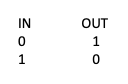

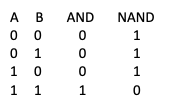

Ang talahanayan ng katotohanan ay ang mga sumusunod:

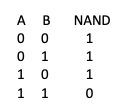

Samantala, ang talahanayan ng katotohanan ng NAND logical function ay ang mga sumusunod:

Kaya, na-verify namin na ito ay, sa katunayan, isang gate ng NAND.

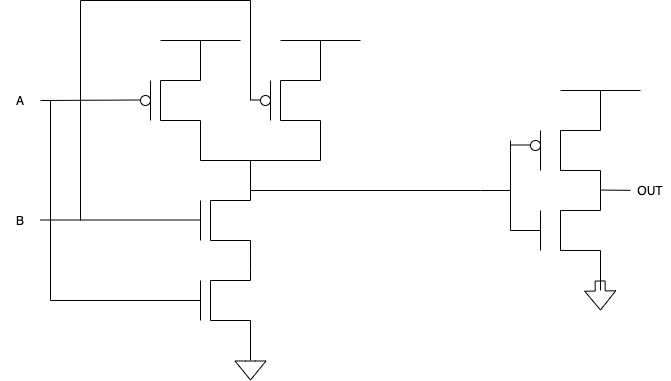

Ngayon, paano tayo gagawa ng AND gate? Buweno, gagawa tayo ng AND gate sa eksaktong paraan kung paano tayo nagtayo ng OR gate mula sa NOR gate! Magkabit kami ng inverter!

Dahil ang lahat ng nagawa namin ay inilapat ang isang NOT function sa isang NAND gate's output, ang talahanayan ng katotohanan ay magiging ganito:

Muli, paki-verify para matiyak na totoo ang sinasabi ko sa iyo.

Ngayon, napag-usapan namin kung ano ang mga pMOS at nMOS transistors pati na rin kung paano gamitin ang mga ito upang bumuo ng mas kumplikadong mga istruktura! Umaasa ako na natagpuan mo ang blog na ito na nagbibigay-kaalaman. Kung gusto mong basahin ang aking mga nakaraang blog, makikita mo ang listahan sa ibaba.